- 您现在的位置:买卖IC网 > Sheet目录2001 > ISL5757IBZ (Intersil)IC DAC 10BIT 260MHZ 28-SOIC

11

FN6078.1

November 12, 2004

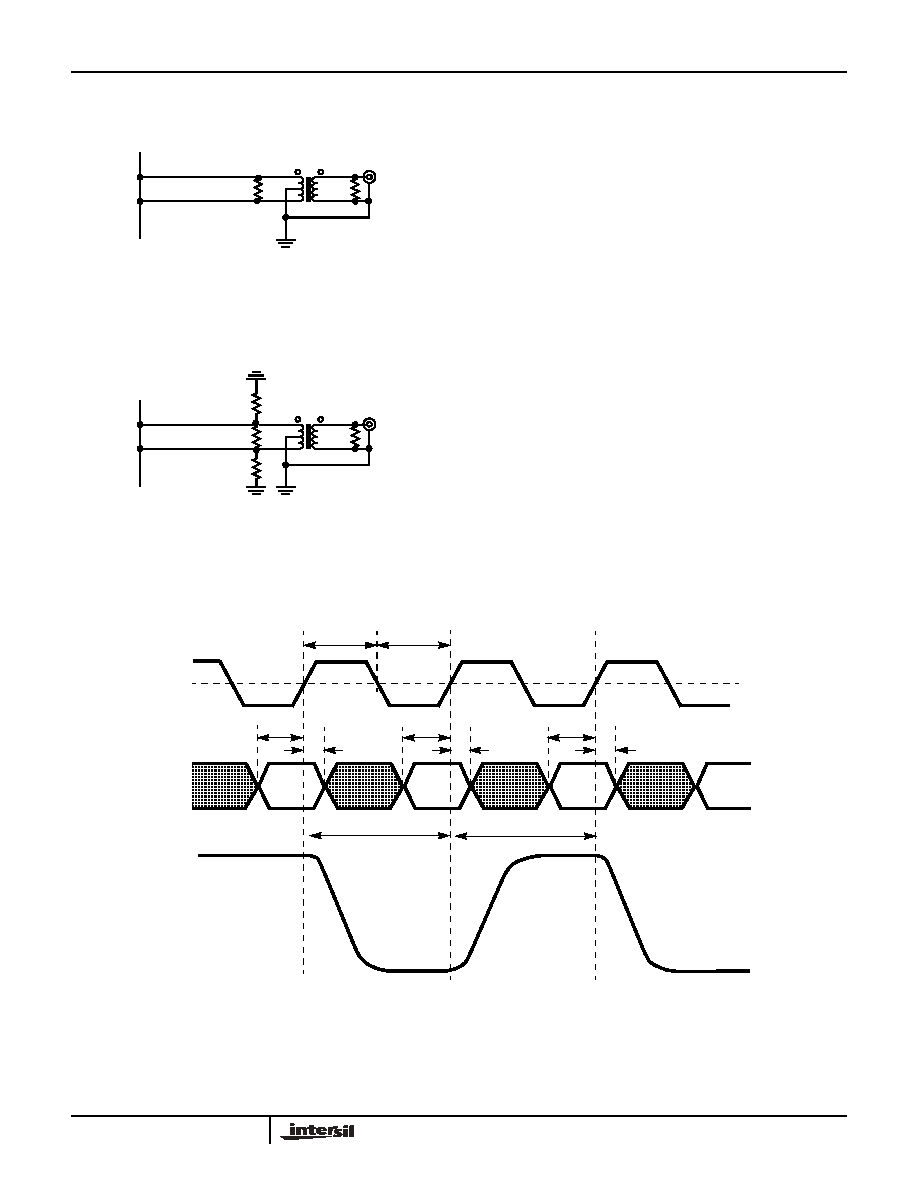

Propagation Delay

The converter requires two clock rising edges for data to be

represented at the output. Each rising edge of the clock

captures the present data word and outputs the previous

data. The propagation delay is therefore 1/CLK, plus <2ns of

processing. See Figure 15.

Test Service

Intersil offers customer-specific testing of converters with a

service called Testdrive. To submit a request, fill out the

Testdrive form. The form can be found by doing an ‘entire

site search’ at www.intersil.com on the words ‘DAC

Testdrive’. Or, send a request to the technical support center.

FIGURE 13. OUTPUT LOADING FOR DATASHEET

MEASUREMENTS

PIN 21

PIN 22

RDIFF

ISL5757

RLOAD

IOUTB

IOUTA

VOUT = (2 x IOUTA x REQ)V

LOAD SEEN BY THE TRANSFORMER

RLOAD REPRESENTS THE

1:1

REQ = 0.5 x (RLOAD//RDIFF)

AT EACH OUTPUT

FIGURE 14. ALTERNATIVE OUTPUT LOADING

PIN 21

PIN 22

ISL5757

IOUTB

IOUTA

VOUT = (2 x IOUTA x REQ)V

REQ = 0.5 x (RLOAD//RDIFF//RA), WHERE RA = RB

AT EACH OUTPUT

RLOAD

RDIFF

RA

RB

LOAD SEEN BY THE TRANSFORMER

RLOAD REPRESENTS THE

Timing Diagram

FIGURE 15. PROPAGATION DELAY, SETUP TIME, HOLD TIME AND MINIMUM PULSE WIDTH DIAGRAM

CLK

IOUT

50%

tPW1

tPW2

tSU

tHLD

tSU

tPD

tHLD

D9-D0

W0

W1

W2

W3

OUTPUT = W0

OUTPUT = W1

tPD

OUTPUT = W-1

ISL5757

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL5761/2IBZ

CONV D/A 10BIT HS LP 28-SOIC

ISL5827INZ

IC DAC DUAL 12BIT 3.3V 48-LQFP

ISL5857IAZ

IC DAC 12-BIT 260MSPS 28-TSSOP

ISL5861/2IBZ

IC DAC 12BIT 210MSPS 28-SOIC

ISL5927INZ

IC DAC 14BIT CMOS DUAL 48LQFP

ISL5929INZ

IC DAC 14BIT CMOS DUAL 48LQFP

ISL5957IBZ

CONV D/A 14-BIT 3.3V 28-SOIC

ISL5961/2IBZ

CONV D/A 14-BIT 3.3V 28-SOIC

相关代理商/技术参数

ISL5761

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:10-bit, +3.3V, 130/210MSPS, CommLink TM High Speed D/A Converter

ISL5761/21A

制造商:Rochester Electronics LLC 功能描述:- Bulk

ISL5761/2IA

功能描述:IC DAC 10BIT 130MSPS 28-TSSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:2,400 系列:- 设置时间:- 位数:18 数据接口:串行 转换器数目:3 电压电源:模拟和数字 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:36-TFBGA 供应商设备封装:36-TFBGA 包装:带卷 (TR) 输出数目和类型:* 采样率(每秒):*

ISL5761/2IAZ

功能描述:CONV D/A 10BIT HS LP 28-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):*

ISL5761/2IB

功能描述:IC DAC 10-BIT 210MSPS 28-SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:2,400 系列:- 设置时间:- 位数:18 数据接口:串行 转换器数目:3 电压电源:模拟和数字 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:36-TFBGA 供应商设备封装:36-TFBGA 包装:带卷 (TR) 输出数目和类型:* 采样率(每秒):*

ISL5761/2IBZ

功能描述:CONV D/A 10BIT HS LP 28-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:1,000 系列:- 设置时间:1µs 位数:8 数据接口:串行 转换器数目:8 电压电源:双 ± 功率耗散(最大):941mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC W 包装:带卷 (TR) 输出数目和类型:8 电压,单极 采样率(每秒):*

ISL5761_04

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:10-bit, +3.3V, 130/210+MSPS, High Speed D/A Converter

ISL57612IA

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:10-bit, +3.3V, 130/210MSPS, CommLink TM High Speed D/A Converter